https://gigazine.net/news/20200717-ddr5-memory-standard/

半導体部品の標準規格を策定する業界団体・JEDECが、DRAMの次世代規格となる「DDR5」の最終仕様を2020年7月14日に発表しました。本来であれば2018年に策定が終了する予定でしたが、「システムメーカーの増大するニーズに対応するために2年以上予定が遅れた」とJEDECは述べています。

JEDEC Publishes New DDR5 Standard for Advancing Next-Generation High Performance Computing Systems | JEDEC

https://www.jedec.org/news/pressreleases/jedec-publishes-new-ddr5-standard-advancing-next-generation-high-performance

DDR5 Memory Specification Released: Setting the Stage for DDR5-6400 And Beyond

https://www.anandtech.com/show/15912/ddr5-specification-released-setting-the-stage-for-ddr56400-and-beyond

JEDECによれば、ダイ面積当たりの最大記憶密度で比較したとき、DDR4が16Gbitsであるのに対し、DDR5は64Gbitsだとのこと。つまり、UDIMMの場合、メモリ1枚の容量がDDR4で32GBだったのが、DDR5だと最大128GBに達します。また、LRDIMMであれば最大容量は2.0TBに達するそうです。

また、入出力ピン当たりのデータ転送速度は、DDR4が仕様上最大3.2Gbpsであるのに対して、DDR5での最大データ転送速度は製品化時点で4.8Gpbs、仕様上で6.4Gbpsになるとのこと。ただし、IT系ニュースメディアのAnand

Techは、公式の最大値である3.2Gbpsを上回るDDR4メモリが登場していることから、DDR5でも同様に仕様最大値を超えるメモリが登場するのではないかと推測しています。

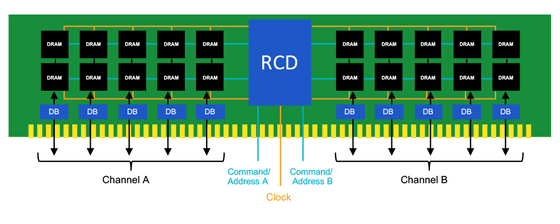

さらに、単一のメモリモジュールが2チャンネルに分割されるようになるのがDDR5の大きな変更ポイント。DDR5はメモリモジュールごとに64ビットデータチャンネルをもつのではなく、DIMMごとに独立した32ビットデータチャンネル、あるいはECCを考慮した場合は40ビットのデータチャンネルをもちます。そして、各チャネルのバースト長がDDR4ではBL8だったのがBL16になり、メモリバンク数も32に倍増。そのため、DDR5の実効帯域幅は、同じメモリクロックのDDR4と比較して2倍になります。

DDR5は動作電圧も下がっており、DDR4では1.2VだったのがDDR5では1.1Vになりました。また、DDR5では、メモリ専用の電圧レギュレーターをマザーボードではなくDIMMに搭載することになりました。この変更により、マザーボードはより簡素な設計が可能になり、生産コストがわずかに削減されるとのこと。なお、DDR5ではピン配置が根本から刷新されたため、DDR5のピン数はDDR4と同じ288ピンですが、互換性はありません。

JEDECは、2021年中にはサーバー向けのDDR5メモリが市場に登場すると予想しており、ライフサイクルはDDR4と同じくおよそ7年とみています。

AMDの計算とグラフィックス部門のジョー・マクリCEOは「ハイパフォーマンスコンピューティングには、今日のプロセッサの増加し続ける要求に対応可能なメモリが必要です。DDR5標準であれば、顧客やエンドユーザーの将来的な需要を満たすために、AMDはより良い製品を設計することができます」とコメントしました。

また、IntelのメモリとIOテクノロジー部門ヴァイル/プレジデントのキャロリン・デュラン氏は「JEDEC の DDR5

規格の発表により、私たちはDDRメモリの性能と機能の新時代を迎えようとしています。業界全体で多大な努力を重ねて開発されたDDR5は、メモリ機能を大きく飛躍させ、AIや高性能コンピューティングの需要に対応するための新技術の登場により、初めて50%増という帯域幅の向上を実現しました」と語っています。